OpenASIP (formerly TTA-based Co-design Environment or TCE) is an open application-specific instruction-set toolset. It can be used to design and program customized compiler-programmable accelerators based on the energy efficient Transport Triggered Architecture (TTA) processor template. Starting from OpenASIP 2.0, it can be also used for RISC-V instruction-set co-design.

OpenASIP (formerly TTA-based Co-design Environment or TCE) is an open application-specific instruction-set toolset. It can be used to design and program customized compiler-programmable accelerators based on the energy efficient Transport Triggered Architecture (TTA) processor template. Starting from OpenASIP 2.0, it can be also used for RISC-V instruction-set co-design.

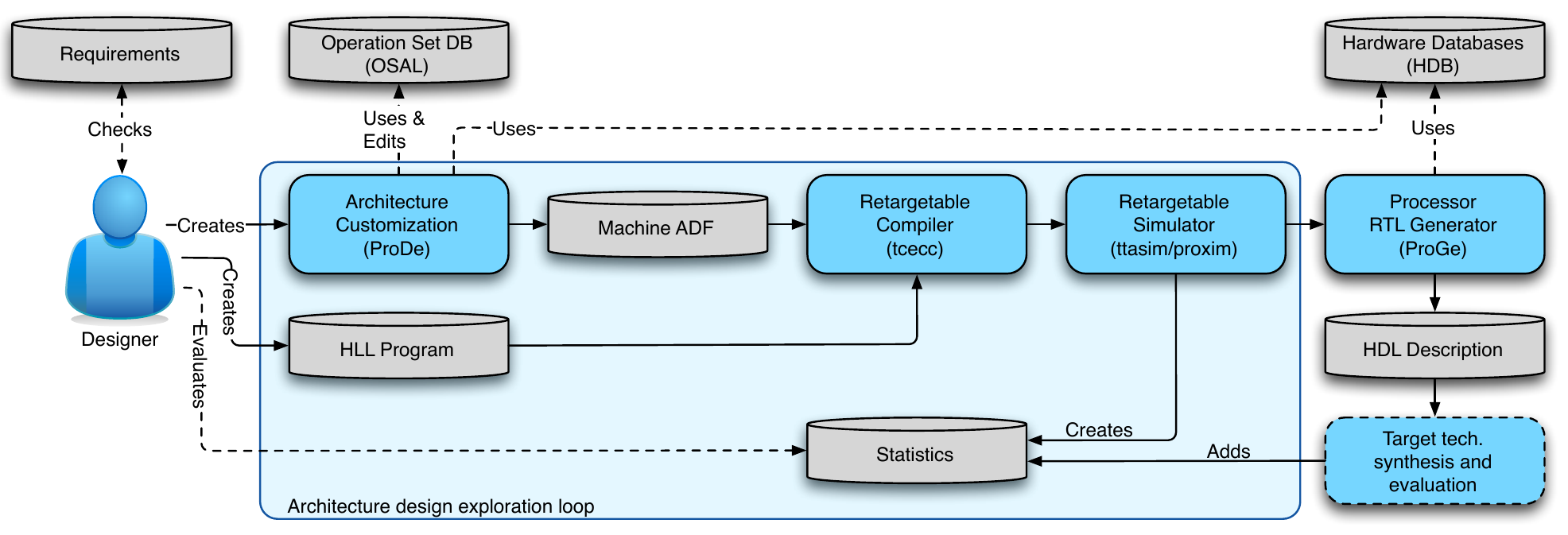

The toolset provides a complete retargetable co-design

flow from high-level language programs down to synthesizable processor

RTL (VHDL and Verilog backends supported) and parallel program binaries.

Processor customization points include the register files, function units,

supported operations, and the interconnection network.

OpenASIP development is led by the Customized Parallel Computing (CPC) group at the Tampere University, Finland. Further reading: LLVM project blog post about OpenASIP.

News and updates

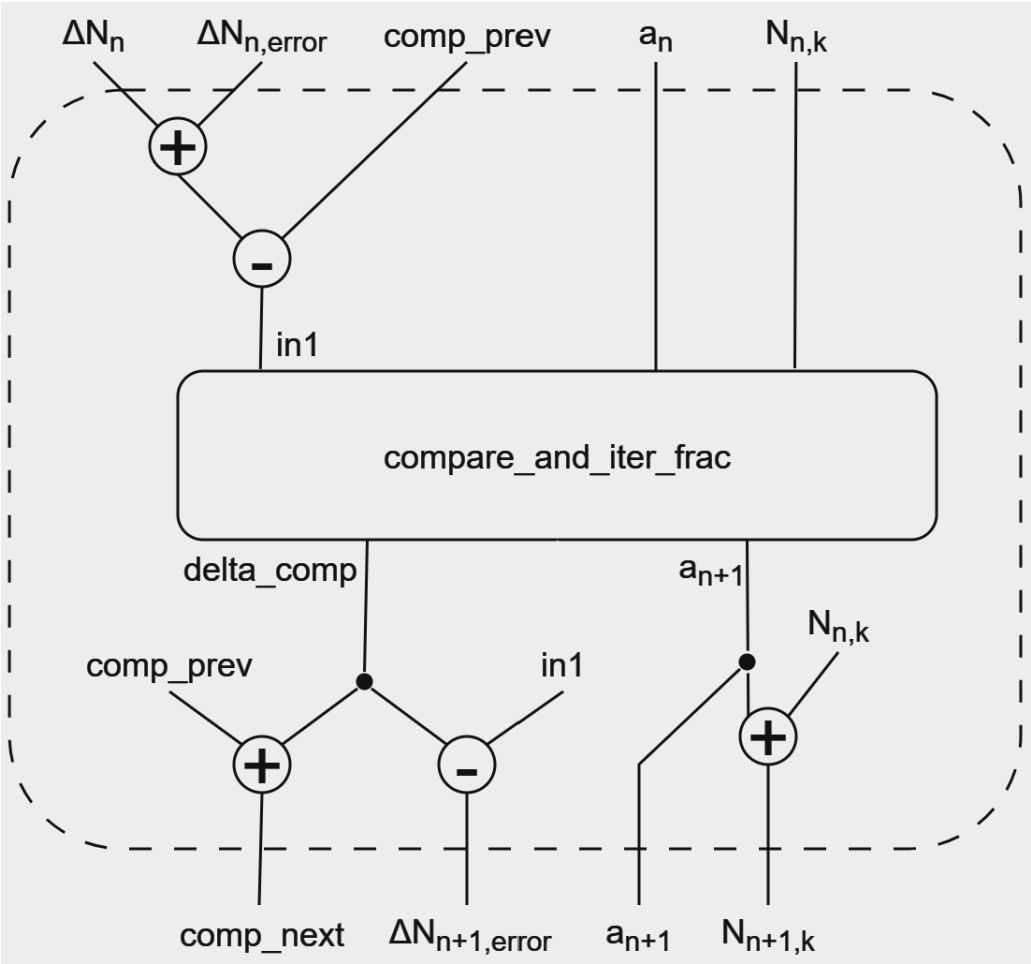

A master's thesis utilizing OpenASIP for the design and programming of an ASIP for medical ultrasound beamforming was published by NTNU. The author demonstrates the benefits of ASIPs by combining instruction set customization and interconnection pruning, yielding promising results in terms of performance, area, and power consumption compared to both OpenASIP-designed baseline processors and related work.

We were happy to see that this design didn’t fall into the common pitfall of TTA designs with a lot of redundant datapath connections. Fully connected buses have been sadly very popular in designs done outside the group - we blame the too easy-to-use “fully connect IC” functionality in the Processor Designer for that! Unfortunately the IC in this design was so heavily optimized that the C compiler couldn’t produce efficient code and the best results were only received via hand coding the processor – something for the future code generation research to improve upon.

Picture from: Gustav Kollstrøm, "Application-Specific Instruction Set Processor for Medical Ultrasound Beamforming", master's thesis, NTNU, 2024

Picture from: Gustav Kollstrøm, "Application-Specific Instruction Set Processor for Medical Ultrasound Beamforming", master's thesis, NTNU, 2024

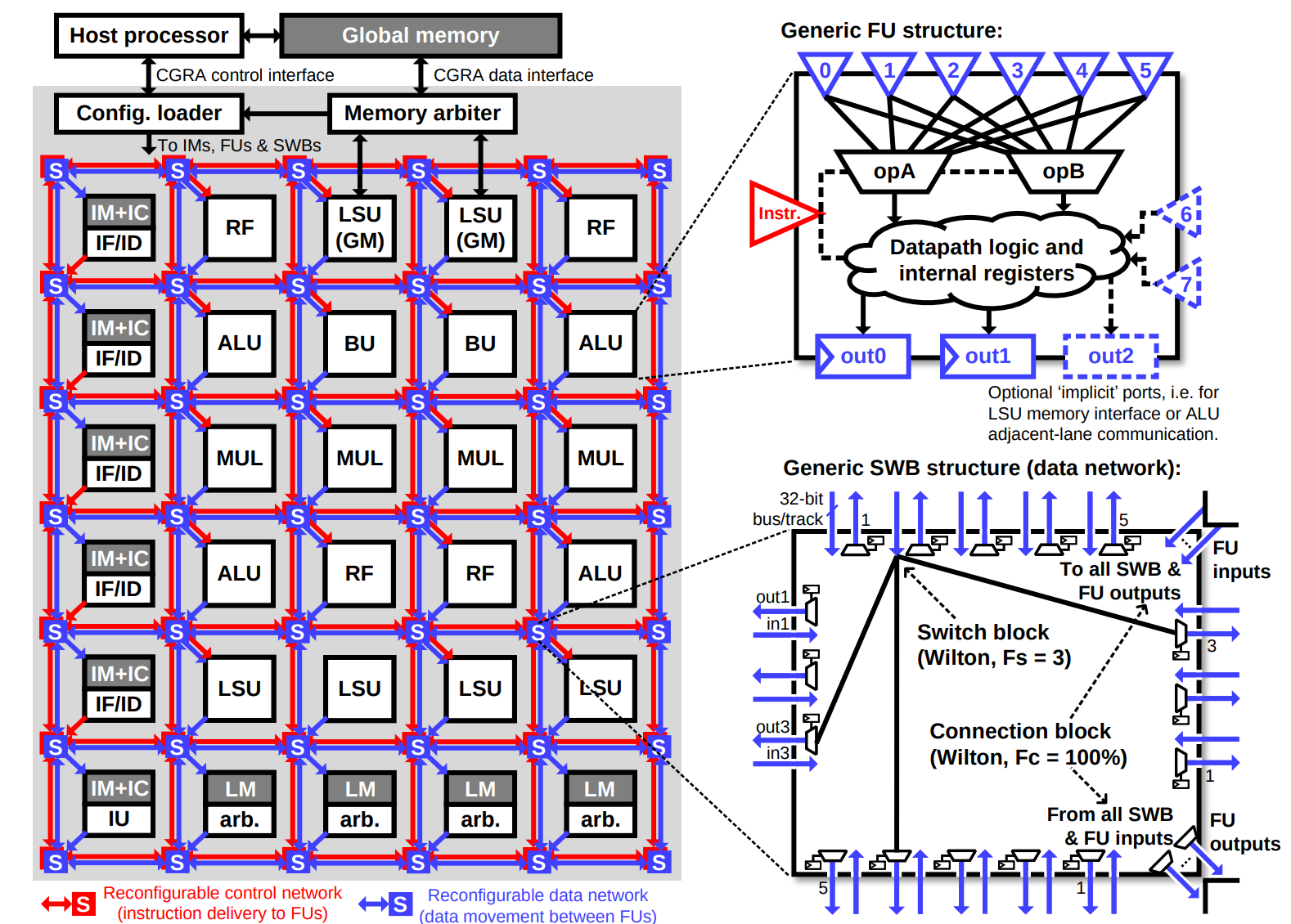

As a result of collaboration between Eindhoven University of Technology, Netherlands and Tampere University, Finland, the work on R-Blocks, an ultra low power coarse-grained reconfigurable array CGRA was published in ACM Transactions on Reconfigurable Technology and Systems (TRETS). CGRAs have been proposed as a flexible yet energy-efficient platform. Thanks to OpenASIP's flexible architecture description template and retargetable compiler, R-Blocks is the first compiler-programmable CGRA. Read the publication here.

In a recent work Yanık et al. used OpenASIP toolset as a basis for rapidly extending the instruction set of RISC-V cores. They use Vitis HLS tool to generate custom function units (FU) directly from C program descriptions. What a great idea! The user needs to only give the description of the custom operation in C and the tools generate a full function unit out of it. After that, their scripts integrate the function unit into a RISC-V ASIP using OpenASIP. It’s great to see how our easy-to-use custom FU integration enables people to create experiments like this. Their paper DELTA-V: An Open-Source High-Level Synthesis Driven ASIP Design Automation Tool for RISC-V Microprocessors was published in 2023 14th International Conference on Electrical and Electronics Engineering (ELECO). The paper is available here and the source code here.

A new version of OpenASIP released! See the change summary for more details. Install instructions can be found in the README.

Interesting audio processor case study designed with OpenaASIP was published by University of Turin researchers who received good results even while using a fully connected interconnection matrix: The power consumption of the developed TTA architecture was found to be significantly lower compared to traditional software-based approaches, with a total estimated power of approximately 350 mW. Details can be found in the publication and the master's thesis.

The first OpenASIP version with preliminary RISC-V customization support is now out!

The slide set (39M) contains clickable videos and goes through most of the tool set. It was first presented in OpenSuco 3 workshop organized within the ISC High Performance 2018 conference (June 28th in Frankfurt, Germany).

A demonstration featuring a neural network coprocessor designed with OpenASIP was shown at CIVIT.

For more info, read the post on the Pervasive Computing blog.

Feature highlights

- Compiler:

- LLVM based, Clang as the default frontend

- OpenCL support via the pocl project

- Basic block instruction scheduler (top-down and bottom-up)

- Delay slot filling

- Software bypassing

- (experimental) Operand sharing

- Custom operation support

- Parallel TTA assembler

- Software and hardware floating point support

- Basic debugging info support

- Multiple address space support

- Support for native computation on half precision floats (fp16)

- Simulator:

- Graphical and command line user interfaces

- Interpretive debugging engine for cycle stepping

- Static compiled engine for fast simulation with basic block granularity (but cycle count accuracy)

- Dynamic compiled engine for improved startup time with fast simulation

- SystemC integration API

- Processor and Program Image Generation:

- Support for generating implementation for the designed processor as VHDL. Experimental support for Verilog.

- Generates bit image of the program (supported formats include the Altera MIF)

- Dictionary-based instruction compression

- Automated generation of the files needed to integrate the core to different FPGA platforms.

- IP-XACT 1.5 support

- Design space exploration:

- Automated, manual and semi-automatic algorithm implementations

- Tools that allow easy modification of the target architecture

- Automated search of the connectivity design space

- Integrated Development Environment tools:

- Graphical user interface (GUI) for editing architecture resources

- GUI for editing operation set definitions